electronics-journal.com

12

'26

Written on Modified on

Hardware Verification Platforms Target Complex AI Chips

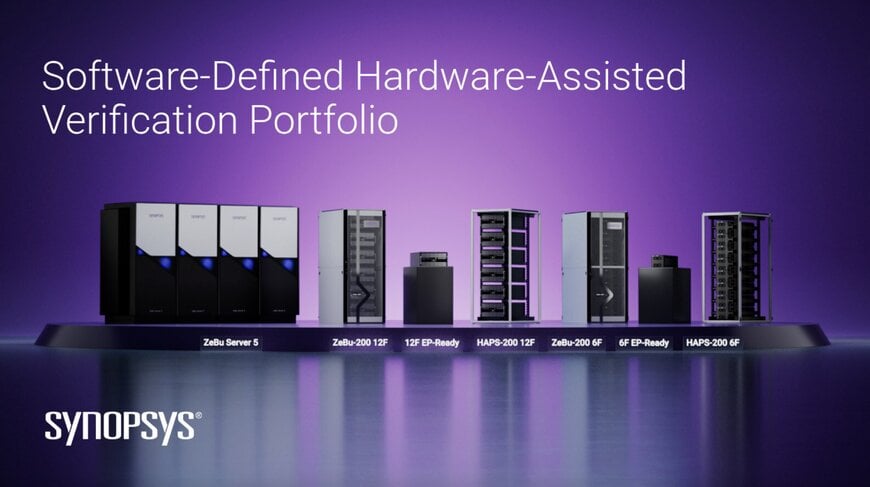

Synopsys expands its hardware-assisted verification portfolio with new ZeBu and HAPS systems designed for large-scale AI chip validation.

www.synopsys.com

Synopsys has introduced new hardware platforms and software capabilities within its hardware-assisted verification (HAV) portfolio to address the increasing complexity of AI chip design. The updated solutions are intended to support verification workflows for multi-die systems and large-scale AI processors used in data centers, edge computing and embedded systems.

The company’s HAV platforms combine hardware emulation, FPGA-based prototyping and software-defined verification capabilities to help semiconductor developers validate system behavior before silicon fabrication.

Rising Complexity in AI Chip Verification

AI processor development is increasing the computational demands of verification processes. Large language models are expanding rapidly in size, while interface data rates and system throughput requirements continue to increase.

These trends require verification systems capable of running extremely large numbers of validation cycles and supporting heterogeneous architectures combining CPUs, GPUs, accelerators and networking processors.

Hardware-assisted verification environments address this challenge by enabling engineers to emulate complete system behavior and test workloads before physical chips are manufactured.

Expanded ZeBu and HAPS Verification Platforms

The latest updates introduce new platforms in the ZeBu and HAPS product families.

The ZeBu Server 5 emulation platform has been enhanced with software-defined updates that increase performance and scalability. The platform is designed to support verification of large AI training and inference systems as well as networking processors such as IPUs and DPUs.

New HAPS-200 and ZeBu-200 systems incorporate up to twelve FPGA devices, providing twice the capacity of earlier six-FPGA platforms. These systems use AMD Versal Premium VP1902 adaptive SoCs to support high-performance emulation and prototyping environments.

Synopsys also introduced a HAPS-200 single-FPGA desktop system intended for IP verification and early software bring-up.

Software-Defined Verification Workflows

The HAV platforms use a software-defined architecture that enables modular hardware configuration and ongoing performance improvements through software updates.

New verification capabilities include hardware-assisted testing tools that automate validation of processor, memory and I/O subsystems under realistic workloads. Engineers can evaluate system behavior across corner cases and perform full-system coherency validation before tape-out.

Real-number modeling support allows analog system behavior to be approximated within digital verification environments, enabling faster testing of mixed-signal designs.

Fault Injection and Reliability Testing

The updated platforms also include expanded fault emulation capabilities. These tools allow engineers to inject faults into simulated systems and analyze how designs respond under error conditions.

Fault emulation supports verification of safety-critical systems and high-reliability electronics where resilience to hardware faults must be validated during development.

By combining hardware emulation, FPGA prototyping and software-defined verification tools, Synopsys aims to enable semiconductor developers to validate increasingly complex AI processors while meeting aggressive product development timelines.

Edited by Industrial Journalist, Romila DSilva - Powered by AI

www.synopsys.com