electronics-journal.com

28

'23

Written on Modified on

KEYSIGHT, SYNOPSYS, AND ANSYS ACCELERATE RFIC SEMICONDUCTOR DESIGN

The new reference flow offers an open, efficient radio frequency design solution using the TSMC N4PRF process.

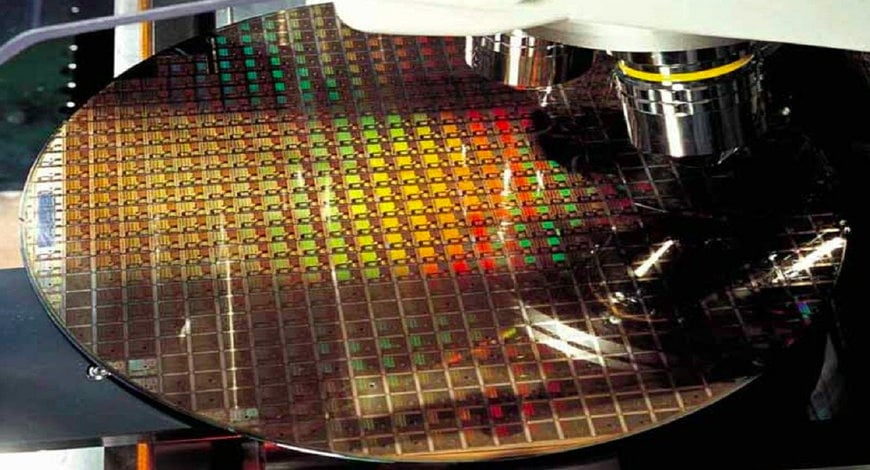

Photo: TSMC

Keysight Technologies, Synopsys, and Ansys announced a new reference flow for the TSMC N4PRF, the world's leading semiconductor foundry's advanced 4 nanometer (nm) radio frequency (RF) FinFET process technology. The reference flow is based on the Synopsys Custom Design Family, which provides a complete RF design solution for customers seeking an open RF design environment with higher predictive accuracy and productivity. It provides designers with a choice of best-in-class solutions and includes validated integrations with radio frequency integrated circuit (RFIC) design and interactive electromagnetic (EM) analysis tools from Keysight and EM modelling and signoff power integrity solutions from Ansys.

Next-generation wireless systems feature higher bandwidth, more connected devices, lower latency, and broader coverage. The design complexity of RF integrated circuits used for wireless data transmission such as transceivers and RF front-end components continues to grow. Higher circuit frequencies, smaller feature sizes, and complex layout-dependent effects make high-speed design physics challenging, requiring more accurate and comprehensive modelling and simulation to achieve the highest performance and robust product reliability.

The TSMC N4PRF design reference flow improves design turnaround time and layout productivity in the Synopsys Custom Compiler™ design and layout environment with rigorous validation using critical design components including low noise amplifiers (LNAs) and LC-tuned voltage-controlled oscillators (LC VCOs). The reference flow features industry-leading tools that enable efficient passive device synthesis, EM model extraction, thermal-aware electromigration analysis extended to include device metal, and post-layout extraction with correct handling of the circuit under inductor (CUI) structures.

In addition to Synopsys Custom Compiler, the open, modern reference flow incorporates:

Signoff accuracy circuit simulation performance from Synopsys PrimeSim™ simulation tools and PrimeSim™ Reliability Environment, and signoff physical verification and extraction solutions from Synopsys IC Validator™ and Synopsys StarRC™.

Ansys Totem™ provides thermal-aware signoff electromigration verification and power integrity analysis (EM/IR). RaptorX™ and Exalto™ provide electromagnetic modeling, with unique CUI features enabling significant area reductions. VeloceRF™ delivers fully automatic silicon layout synthesis for electromagnetic devices including multi-layer inductor spiral, baluns/transformers, and transmission lines.

Keysight PathWave ADS RFPro provides rapid, interactive EM-circuit co-simulation and analysis to find and fix layout-dependent effects up front in the development cycle. PathWave RFIC design (GoldenGate) supports harmonic balance simulation in early chip design and verification process.

Keysight Technologies, Synopsys, and Ansys announced a new reference flow for the TSMC N4PRF, the world's leading semiconductor foundry's advanced 4 nanometer (nm) radio frequency (RF) FinFET process technology. The reference flow is based on the Synopsys Custom Design Family, which provides a complete RF design solution for customers seeking an open RF design environment with higher predictive accuracy and productivity. It provides designers with a choice of best-in-class solutions and includes validated integrations with radio frequency integrated circuit (RFIC) design and interactive electromagnetic (EM) analysis tools from Keysight and EM modelling and signoff power integrity solutions from Ansys.

Next-generation wireless systems feature higher bandwidth, more connected devices, lower latency, and broader coverage. The design complexity of RF integrated circuits used for wireless data transmission such as transceivers and RF front-end components continues to grow. Higher circuit frequencies, smaller feature sizes, and complex layout-dependent effects make high-speed design physics challenging, requiring more accurate and comprehensive modelling and simulation to achieve the highest performance and robust product reliability.

The TSMC N4PRF design reference flow improves design turnaround time and layout productivity in the Synopsys Custom Compiler™ design and layout environment with rigorous validation using critical design components including low noise amplifiers (LNAs) and LC-tuned voltage-controlled oscillators (LC VCOs). The reference flow features industry-leading tools that enable efficient passive device synthesis, EM model extraction, thermal-aware electromigration analysis extended to include device metal, and post-layout extraction with correct handling of the circuit under inductor (CUI) structures.

In addition to Synopsys Custom Compiler, the open, modern reference flow incorporates:

Signoff accuracy circuit simulation performance from Synopsys PrimeSim™ simulation tools and PrimeSim™ Reliability Environment, and signoff physical verification and extraction solutions from Synopsys IC Validator™ and Synopsys StarRC™.

Ansys Totem™ provides thermal-aware signoff electromigration verification and power integrity analysis (EM/IR). RaptorX™ and Exalto™ provide electromagnetic modeling, with unique CUI features enabling significant area reductions. VeloceRF™ delivers fully automatic silicon layout synthesis for electromagnetic devices including multi-layer inductor spiral, baluns/transformers, and transmission lines.

Keysight PathWave ADS RFPro provides rapid, interactive EM-circuit co-simulation and analysis to find and fix layout-dependent effects up front in the development cycle. PathWave RFIC design (GoldenGate) supports harmonic balance simulation in early chip design and verification process.

www.keysight.com